# Hardware & Semiconductor Startups: How to Build a Fundable Deeptech Roadmap

The semiconductor renaissance is here. As AI workloads explode and edge computing becomes ubiquitous, hardware startups are experiencing a once-in-a-generation opportunity. Yet capital remains scarce for those who cannot articulate a crisp, de-risked path from prototype to production. This playbook distills battle-tested strategies for deeptech founders navigating the treacherous waters of Series A fundraising in 2026 and beyond.

# The New Hardware Gold Rush: Why 2026 Is Different

Global semiconductor revenue is projected to surpass \$650 billion by 2027, driven by insatiable demand for inference accelerators, edge AI processors, and next-generation datacentre silicon. Unlike the mobile computing wave of the 2010s, today's opportunity centres on specialised architectures optimised for transformer models, vector processing, and ultra-low-latency inference. NVIDIA's dominance in training hardware has created a massive white space for inference-optimised solutions that deliver 10x better performance-per-watt at fraction of the cost.

What makes 2026 fundamentally different is the maturation of chiplet ecosystems, advanced packaging technologies like CoWoS and EMIB, and the emergence of sovereign semiconductor initiatives across Europe, India, and Southeast Asia. Foundry capacity constraints that plagued 2021-2023 have eased, with TSMC, Samsung, and Intel each adding significant advanced node capacity. Meanwhile, open standards like UCle and CHIPS Alliance are lowering integration barriers, allowing startups to focus on differentiated IP rather than reinventing entire system architectures.

Strategic corporate venture arms from systems integrators, cloud hyperscalers, and automotive OEMs are actively scouting for next-generation silicon. But they demand more than elegant architecture diagrams. Investors want proof of systematic de-risking, partnership momentum, and a credible path to tape-out within 18-24 months. The question is no longer "can you design a chip?" but rather "can you deliver silicon that solves a \$100M+ problem for a design partner willing to co-invest in your success?"

# The Fundability Framework: Four Pillars Every Investor Scrutinises

## Technical De-Risking

FPGA validation, tape-out roadmap, silicon partners identified

Elite venture firms applying McKinsey-grade diligence assess semiconductor startups through a ruthlessly systematic lens. Technical brilliance is table stakes. What separates fundable companies from science projects is a demonstrated ability to navigate the treacherous journey from RTL to revenue.

## Commercial Validation

Letters of intent, pilot programmes, revenue commitments

The most successful hardware founders in 2026 treat their roadmap as a living strategic document, updated quarterly with gating milestones that systematically retire technical, commercial, and operational risks. Each milestone should have clear success criteria, fallback options, and explicit linkage to the next financing round.

## Ecosystem Alignment

Foundry relationships, packaging partners, software stack maturity

## Capital Efficiency

Milestone-based financing, non-dilutive funding secured

# Roadmap Gating: Converting R&D Into Investment-Grade Milestones

# The Partnership Imperative: Why Solo Tape-Out Is Fundraising Suicide

## Foundry & Ecosystem Partnerships

### Foundry Relationship

Secure multi-project wafer access or shuttle run commitment from TSMC, Samsung, GlobalFoundries, or emerging players like Tower, UMC. Demonstrate you understand PDK constraints and have design rule check flows validated.

### Packaging Partners

Advanced packaging is now the performance bottleneck. Establish relationships with OSAT providers (ASE, Amkor, JCET) or in-house packaging groups at foundries for CoWoS, InFO, or 3D stacking capabilities.

### Design IP Ecosystem

Leverage proven IP blocks for SerDes, memory controllers, and power management from Synopsys, Cadence, or ARM rather than custom design. Investors view this as capital efficiency and risk mitigation.

### Software Stack Maturity

Hardware without software is a doorstop. Demonstrate compiler support, driver maturity, and integration into customer frameworks (TensorRT, PyTorch, ONNX). Open-source your toolchain early to build developer mindshare.

No semiconductor startup has successfully scaled without deep, strategic partnerships across the value chain. The days of vertically integrated semiconductor companies are largely over outside of a few hyperscale players. Investors want to see that you have secured commitments from foundry partners, packaging providers, and critically, systems integrators who will help you navigate the treacherous path from first silicon to production qualification. These partnerships serve as powerful de-risking signals and can dramatically compress your time to market while preserving capital.

# Customer-Backed Deliverables: The Ultimate Fundraising Accelerant

## What Investors Want to See

Letters of intent with volume commitments, pilot service-level agreements with acceptance criteria, joint development agreements with shared IP rights, or better yet — purchase orders with milestone-based payments.

## From Science Project to Viable Business

The single most powerful lever for increasing valuation and reducing dilution is demonstrating that sophisticated customers are willing to bet their own roadmaps on your success. A credible letter of intent from a Tier 1 cloud provider, automotive OEM, or telecommunications infrastructure vendor can increase your valuation by 2-3x and compress your fundraising timeline from six months to six weeks.

The key is structuring these customer relationships to align incentives. The most sophisticated founders negotiate joint development agreements where the customer provides engineering resources, early feedback on silicon, and commits to volume purchases contingent on meeting mutually agreed performance benchmarks. This transforms your R&D from speculative investment into customer-funded product development — a fundamentally different risk profile that sophisticated VCs reward handsomely.

# Milestone De-Risking: A Practical Checklist for Seed Through Series A

01

## Seed Stage (Architecture Validation)

FPGA prototype demonstrating core architecture, early customer discovery with 3-5 design partners, competitive benchmarking on reference workloads, initial foundry conversations, experienced chip design team assembled

02

## Pre-Series A (Tape-Out Readiness)

RTL freeze with DFT sign-off, foundry partnership formalised with PDK access, packaging strategy defined with provider selected, software stack alpha release, letter of intent from lead design partner

03

## Series A (First Silicon)

Successful tape-out with first silicon in hand, bring-up completed with key functions validated, pilot deployment at 1-2 customers, software stack beta release with customer integration, line-of-sight to production qualification

04

## Series B+ (Production Scaling)

Volume production with multiple customers, gross margins validated at scale, next-generation architecture in RTL, established revenue trajectory supporting path to profitability

Each financing milestone should represent a fundamental reduction in technical and commercial risk. Seed capital is deployed to prove your architecture solves a real problem better than alternatives. Series A capital funds tape-out and first silicon bring-up while expanding your design partner pipeline. Series B is about scaling production and demonstrating repeatable go-to-market. Founders who blur these stages or attempt to telescope milestones inevitably create valuation challenges and extend fundraising timelines.

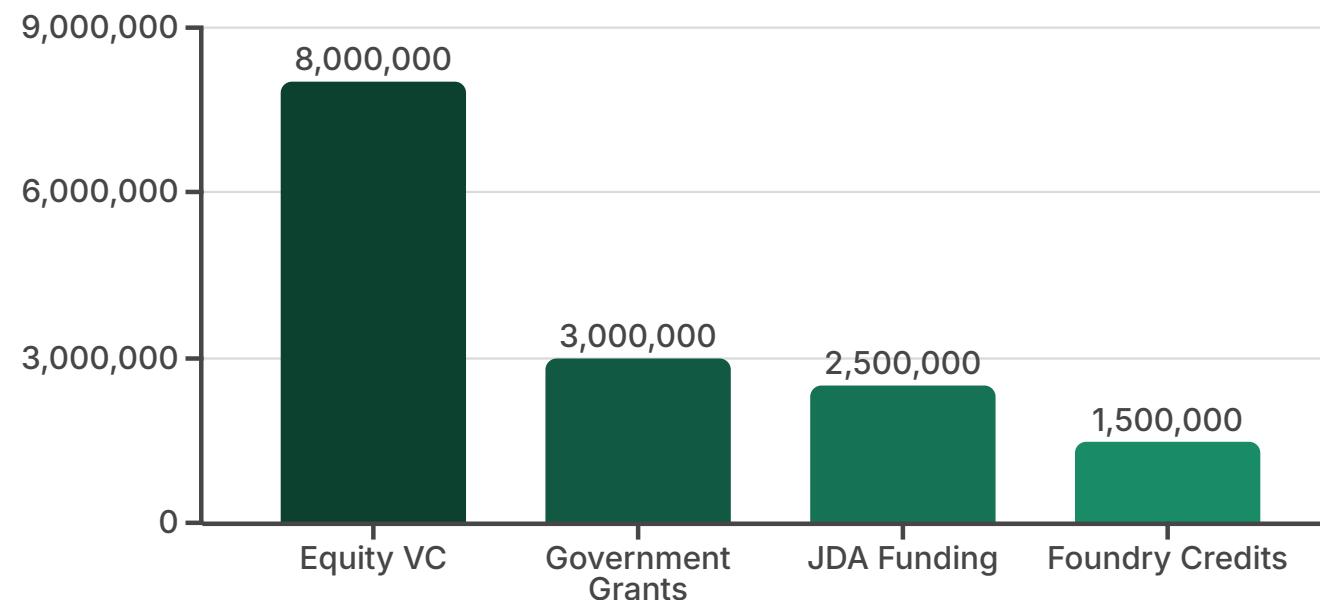

# Non-Dilutive Funding: The Hidden Weapon for Capital Efficiency

## Government & Strategic Capital Sources

The global semiconductor landscape has been reshaped by sovereign initiatives pouring over \$400 billion into domestic chip production. India's Semicon India programme, the US CHIPS Act, EU Chips Act, and similar programmes in Japan, Korea, and Taiwan offer unprecedented non-dilutive funding for qualifying startups. These programmes typically provide grants, tax incentives, and low-cost loans that can fund 25-40% of your tape-out costs.

Beyond government programmes, strategic corporate venture arms from systems OEMs, foundries, and cloud providers increasingly offer non-dilutive development funding through joint development agreements. A well-structured JDA can provide engineering resources, foundry subsidies, and early revenue that dramatically extends your runway between equity rounds. The most sophisticated founders layer multiple funding sources — government grants covering foundry costs, customer-funded development agreements, and equity capital reserved for team expansion and go-to-market.

# Future Vision: The Semiconductor Startup Landscape in 2027-2030

The next four years will witness a fundamental transformation in how semiconductor startups are built and financed. Three mega-trends will reshape the landscape. First, the transition to chiplet-based architectures will dramatically lower barriers to entry. Startups will increasingly focus on differentiated compute tiles while leveraging commodity I/O, memory, and power management chiplets from the ecosystem. This will compress development timelines from 36 months to 18 months and reduce capital requirements by 40-50%.

Second, the emergence of AI-native EDA tools will revolutionise chip design productivity. Generative AI for RTL generation, automated physical design, and intelligent verification are already reducing design team sizes and accelerating iteration cycles. By 2028, we expect seed-stage startups to achieve tape-out readiness with teams of 8-12 engineers rather than 20-30, fundamentally changing the capital efficiency equation and enabling a new generation of lean deeptech companies.

Third, the regionalisation of semiconductor supply chains will create new opportunities for startups aligned with domestic manufacturing ecosystems. India's emergence as a semiconductor design hub, coupled with government incentives and growing domestic demand from electronics manufacturing, positions Indian deeptech founders uniquely well. The combination of world-class engineering talent, competitive labour costs, and strategic government support creates a compelling arbitrage for global investors seeking exposure to the next semiconductor champions. Startups that thoughtfully navigate this landscape — building chiplet-compatible architectures, leveraging AI-native tools, and securing strategic partnerships with domestic fabs and systems integrators — will command premium valuations and accelerated paths to liquidity.

# Your Roadmap to Fundability: Executive Action Items

## Milestone Mapping

Restructure your roadmap with clear technical and commercial gates. Each milestone should retire specific risks and enable the next financing round.

## Partnership Blitz

Launch a 90-day partnership sprint to secure foundry access, packaging commitments, and design partner letters of intent.

## Customer Validation

Convert your top 3 prospects into formal pilot agreements with measurable success criteria and volume commitments.

## Funding Stack

Layer non-dilutive capital from government programmes and JDAs to reduce equity dilution by 30-40% per round.

## Investor Narrative

Craft a data-driven pitch that quantifies risk reduction at each milestone and demonstrates clear path to \$100M+ revenue.

The semiconductor opportunity of the 2020s is real, substantial, and accessible to well-prepared founders. But capital flows to those who demonstrate mastery of both technology and business strategy. Your technical differentiation is necessary but insufficient. Investors back teams who systematically de-risk their path to production, build deep ecosystem partnerships, and secure customer commitments that transform R&D into customer-funded development. Execute this playbook with precision, and you will not only secure funding — you will build a category-defining semiconductor company positioned to capture billions in value as AI and edge computing reshape the global economy. The moment is now. The question is whether you will seize it with strategic clarity and operational excellence.

# XBridge: Shaping Tomorrow's Leaders

## The future belongs to those who shape it. We help you lead the way.

XBridge partners with visionary leaders to navigate complexity and build decisive advantage for the next decade.

### Who We Are

We guide founders, leaders, and enterprises through complexity, designing enduring systems that build decisive advantage. We don't chase fleeting trends; we forge lasting impact.

**Vision** Define clear, actionable futures

**Action** Execute with deliberate, proactive steps

**Creation** Innovate new paths and effective solutions

**Adaptation** Persist and thrive through change

**Clarity, not noise, defines leadership in the next decade.**

### What Sets Us Apart

#### Strategic Clarity

We distill ambiguity into decisive, actionable plans for effective leadership.

#### Brand as Driver

Your brand isn't just aesthetic; it's a powerful business driver.

#### Impactful Intelligence

Every insight is crafted to influence markets, empower teams, and boost revenue.

### Services

- Strategic & Brand Audits

- Brand Strategy Reports

- Growth & Experience Diagnostics

- Leadership Development

- Advisory for AI-native & Future-Ready Businesses

### Who We Serve

XBridge partners with leaders committed to long-term vision and decisive action. We serve founders, growth-stage companies, strategic operators, and established enterprises navigating the next decade.

Ready to begin? Start with an Audit.